# Comprehensive Physical Model of Dynamic Resistive Switching in an Oxide Memristor

Sungho Kim, ShinHyun Choi, and Wei Lu\*

Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, Michigan 48109, United States

**ABSTRACT** Memristors have been proposed for a number of applications from nonvolatile memory to neuromorphic systems. Unlike conventional devices based solely on electron transport, memristors operate on the principle of resistive switching (RS) based on redistribution of ions. To date, a number of experimental and modeling studies have been reported to probe the RS mechanism; however, a complete physical picture that can quantitatively describe the dynamic RS behavior is still missing. Here, we present a quantitative and accurate dynamic switching model that not only fully accounts for the rich RS behaviors in memristors in a unified framework but also provides critical insight for

continued device design, optimization, and applications. The proposed model reveals the roles of electric field, temperature, oxygen vacancy concentration gradient, and different material and device parameters on RS and allows accurate predictions of diverse set/reset, analog switching, and complementary RS behaviors using only material-dependent device parameters.

KEYWORDS: memristor · physical model · drift · diffusion · oxygen vacancy

he rapid advances in digital electronic devices in the past few decades have brought significant changes to society. Generally, digital devices such as field-effect transistors can retain two discrete stable states, "0" and "1", and fast and abrupt transitions between the two states have been regarded as an essential prerequisite for reliable device operation. However, as power consumption becomes a major bottleneck for current digital computing systems based on the von Neumann architecture, alternative computing technologies have begun to attract attention in recent years, such as neuromorphic systems and analog arithmetic computing schemes. Neuromorphic computing is a bioinspired approach that could be more energyefficient than the conventional Boolean logic computation due to its parallelism, while offering other attractive features such as fault tolerance.<sup>1–5</sup> Additionally, arithmetic operations based on analog memories also present an attractive computation paradigm to complement digital von Neumann computations in the future.<sup>6</sup>

Memristors are two-terminal electrical devices whose resistances are modulated

through the dynamic evolution of a set of internal state variables.<sup>7–9</sup> They have been extensively studied for nonvolatile memory storage, neuromorphic computing, and implementation logic applications.4,5,10-13 However, although a number of models have been proposed to describe the device behavior, they are either nondynamic and can only predict steady-state properties<sup>14</sup> or oversimplified.<sup>9,15–19</sup> Providing a dynamic memristor model that can accurately explain the rich memristive switching behaviors not only fills an urgent need that enables accurate simulation of large-scale memristor systems but also can significantly improve our understanding of the different factors that drive the switching process and will be critical for continued optimization and design of this important class of devices.

In this work, we present a complete physical model that quantitatively and accurately describes the rich memristive switching behaviors in a tantalum-oxide-based bilayer memristor. As memory devices, tantalum-oxide-based memristors have shown excellent switching performance between two discrete resistance levels, including \* Address correspondence to wluee@eecs.umich.edu.

Received for review November 10, 2013 and accepted February 26, 2014.

Published online February 26, 2014 10.1021/nn405827t

© 2014 American Chemical Society

VOL.8 • NO.3 • 2369-2376 • 2014

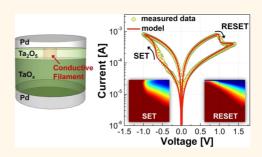

Figure 1. Modeling a tantalum oxide memristor during set/reset. (a) Schematic and cross-sectional TEM images of the Pd/ Ta<sub>2</sub>O<sub>5</sub>/TaO<sub>x</sub>/Pd bilayer memristor device. (b) Measured and calculated DC I-V characteristics of the Pd/Ta<sub>2</sub>O<sub>5</sub>/TaO<sub>x</sub>/Pd device. The measured device size is 50 nm  $\times$  50 nm, and the voltage sweep speed is 2 V/s. (c) Calculated 2-D maps of  $n_D$  as well as (d) 1-D profiles of  $n_{\rm D}$  along the center of the CF in the initial state, after reset, and after the set process. The depleted gap is defined as the position where  $n_D$  is below 5  $\times$  10<sup>20</sup> cm<sup>-3</sup>. The z = 0 position is the Ta<sub>2</sub>O<sub>5</sub>/TaO<sub>x</sub> interface.

extreme cycling endurances of over 10<sup>12</sup> cycles and fast switching speeds below 10 ns.<sup>20,21</sup> By solving the dynamic transport equations of oxygen vacancies, we can precisely predict the resistive switching behaviors in tantalum-oxide-based memristors in both DC and pulse operation modes using a single set of materialdependent parameters. More importantly, analog switching behaviors were also observed in the simulation and confirmed experimentally. Our quantitative analysis reveals that the SET process is driven by both the electric field and thermal effects, while RESET is mainly driven by thermal effects. Furthermore, rich dynamic switching processes including complementary resistive switching (CRS) and different analog switching properties in the memristor can be fully accounted for by considering the competition of diffusion, drift, and thermophoresis effects, using only one set of material-specific parameters.

## **RESULTS AND DISCUSSION**

The tantalum-oxide-based bilayer memristor consists of a highly resistive Ta<sub>2</sub>O<sub>5</sub> layer on top of a less resistive TaO<sub>x</sub> base layer (see Supporting Information) sandwiched by top and bottom Pd electrodes (TE and BE),<sup>22</sup> as shown in Figure 1a. To explain the resistive switching behaviors, the concept of the formation/ rupture of conductive filaments (CFs) has been generally accepted.<sup>23</sup> Here the filaments correspond to regions with high oxygen vacancy ( $V_{O}$ ) concentration so the local electrical conduction becomes metallic.<sup>24</sup> The device can be set (from a low conductance state to a high conductance state) or reset (from a high

conductance to a low conductance) among different resistance states by controlling the properties (e.g.,  $V_{\Omega}$ concentration and shape) of the filament. The simulation starts immediately after the electroforming process, where a continuous CF has connected the TE and  $TaO_x$  layer (Figure 1c). The dynamic resistance switching processes are driven by  $V_{\Omega}$  migration through three factors: the local electric field, the  $V_{\Omega}$  concentration gradient, and the temperature gradient due to Joule heating.<sup>23–25</sup> Thus, the complete memristive switching process can be captured after self-consistent solving three partial differential equations (PDEs) following an approach first proposed by lelmini et al.:<sup>19,25,26</sup> (1) a drift/diffusion continuity equation for  $V_{\Omega}$  transport (Supporting Information eq 1), (2) a current continuity equation for electrical conduction (Supporting Information eq 2), and (3) a Fourier equation for Joule heating (Supporting Information eq 3), as summarized in Figure S2. These three PDEs were self-consistently solved here through a numerical solver (COMSOL) to calculate the  $V_{\rm O}$  concentration  $n_{\rm D}$ , electrostatic potential  $\psi_{t}$  and local temperature T. The details for the proposed model are discussed in Supporting Information (Figures S2–S4).

Figure 1b shows the measured and calculated DC I-V characteristics during the set and reset processes. The reset transition starts near 0.9 V. The resistance gradually increases and finally reaches a resistance roughly one decade higher after reset. Similarly, the set transition occurs at a negative voltage and recovers the original lower resistance. Both the calculated reset and set processes are accurately captured by

VOL.8 • NO.3 • 2369-2376 • 2014

IAI

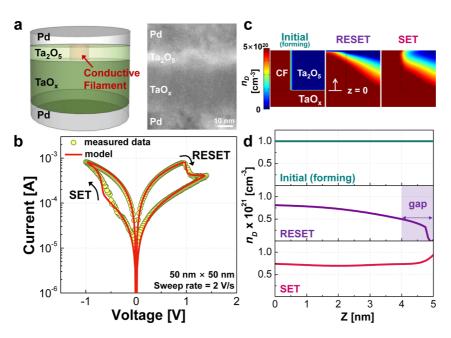

Figure 2. Gradual reset process. (a) Measured and calculated I-V curves, showing the reset transition, obtained by varying  $V_{stop}$  (1.0, 1.2, and 1.4 V). The measured device size is 100 nm  $\times$  100 nm, and the voltage sweep speed is fixed to 2 V/s. (b) Calculated 2-D maps of  $n_D$  as well as 1-D profiles of  $n_D$  corresponding to the different  $V_{stop}$  values.

the model, as shown in Figure 1b. The physical nature of the set and reset processes can be studied by examining the  $n_D$  profiles, as shown in Figure 1d. Specifically, a gap of  $\sim 1$  nm with a depleted  $V_{\Omega}$  concentration was formed near the TE during reset, leading to the increase of the device resistance, while refilling the gap during set leads to the recovery of the high conductance. In addition, by controlling the maximum reset voltage  $V_{\text{stop}}$ , different resistance values can be obtained and have been measured experimentally, as shown in Figure 2a. The model accurately reproduces the gradual reset transition behavior with different values of  $V_{\rm stop}$ and reveals that the different resistance levels when using different  $V_{\text{stop}}$  corresponds to the modulation of the length of the depleted gap,<sup>10,25</sup> as shown in Figure 2b. The ability to obtain different resistance values is necessary for multilevel storage in memory applications and for emulating analog weights in neuromorphic computing. By accurately capturing the resistive switching behaviors, the model further reveals the key enabling factors for multilevel switching. Specifically, the effects of different material and device parameters, for example, the TE material, oxide thickness, the activation energy  $E_{a}$ , and characteristic hopping distance a for  $V_{\Omega}$  migration, have been thoroughly examined (see Supporting Information).

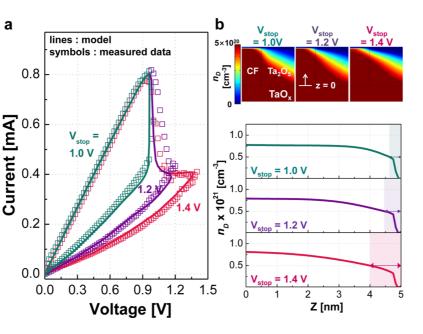

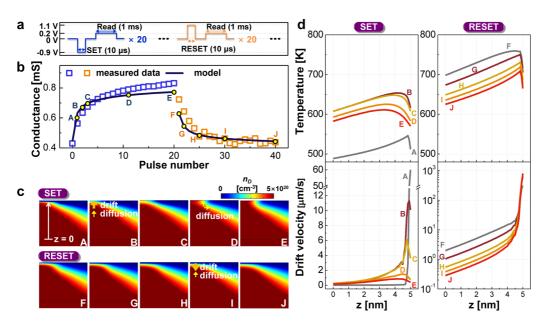

By accurately capturing the internal device dynamics, the proposed model not only reproduces the DC characteristics but also accurately captures timedependent AC characteristics using the same set of material-dependent parameters. Below we show the experimental and simulation results focusing on pulseprogrammed analog switching behaviors. Figure 3a shows the schematic of the pulse trains used for the measurements. Each pulse train consists of 20 set or reset pulses (-0.9 and 1.1 V, respectively) followed by small, nonperturbative read voltage pulses (0.2 V, 1 ms) in the intervals. Figure 3b shows the measured and the simulated conductance values during the applied pulse trains (the measured transient responses as a function of time is shown in Figure S5). A gradual transition in both the set and reset responses is clearly observed as the number of applied pulse increases, which is distinct from the previously discussed abrupt resistive switching behaviors in tantalum oxide.<sup>20</sup> The simulated results for the analog switching behavior also match very well with the measured data for both the set and reset pulse trains.

The accurate model allows us to gain insight into the factors affecting analog switching in oxide memristor devices. Figure 3c shows the calculated 2-D maps of  $n_{\rm D}$ , and Figure 3d shows the calculated temperature T and  $V_{\rm O}$  drift velocity v at the center of the filament, at different points during the consecutive set/reset pulses. First, an abrupt transition occurs within the third set pulse (states A-C). At the starting point of the set period, the temperature inside the CF is lower than that reached during the reset pulse since the filament is not yet complete. Nevertheless, a sizable temperature increase may still be achieved locally (e.g., local temperature of 500-600 K shown in Figure 3d). Consequently, the  $V_{\rm O}$  drift velocity v is significantly enhanced due to both the strong electric field localized inside the depleted gap and the temperature increase. As a result, the refilling of the gap is dominated by the vertical Vo drift flux. However, after the CF is completed at state C, the drift velocity v quickly decreases due to the reduction of the electric field. Nevertheless, the

VOL.8 • NO.3 • 2369-2376 • 2014

Figure 3. Analog switching behaviors. (a) Schematics of the applied pulse trains used for the measurement of analog switching behavior. Each pulse train consists of 20 set or reset pulses (-0.9 and 1.1 V, 10  $\mu$ s) followed by small, nonperturbative read voltage pulses (0.2 V, 1 ms) in the intervals. (b) Measured and calculated device conductance changes, where the conductance was measured during the read pulse and plotted as a function of applied pulse number. (c) Calculated 2-D maps of  $n_D$  and (d) T and v at different points in the consecutive pulse trains (set pulses are states A–E, reset pulses are states F–J).

continued V<sub>O</sub> diffusion flux allows the diameter of the CF to increase continuously during subsequent set pulses (states D and E, Figure 3c). Accordingly, the internal  $V_{\Omega}$  distribution of the CF follows a two-step process during the set process: (1) initial vertical gap filling by the field and thermal-driven migration of  $V_{\rm O}$ and (2) subsequent lateral expansion of the CF by diffusion. In addition, the depleted gap is localized at the point of maximum temperature, which depends on the structure of the device (whether it is a bilayer or single-layer memristor) and/or the thermal properties of the TE material.<sup>26</sup> In the case of the tantalum oxide bilayer memristor, the position near the TE is the hottest point during reset, and consequently, the depleted gap originates at this location during reset and is refilled during set, while the rest of the device regions experiences relatively little changes (Figure 3c).

A more gradual transition was also observed during reset (states F–J). Since the CF is initially connected during reset, the local temperature inside the filament can increase significantly due to Joule heating. This high temperature leads to simultaneous increases in both the drift and diffusion fluxes, but these two processes tend to have opposite directions during reset. Consequently, although the  $V_0$  drift velocity v is 10 times greater in the reset process than in the set process (Figure 3d) due to the higher temperature, a more gradual transition occurs during the reset process because the drift and diffusion fluxes partially cancel each other. In other words, to optimize the analog switching behavior, tuning the balance between the drift and diffusion fluxes is crucial.

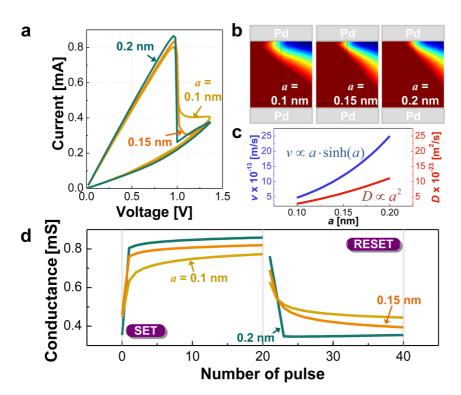

In particular, sudden Vo migration will occur during reset when this balance is disrupted and one flux becomes much larger than the other, and abrupt resistance switching instead of analog switching behavior will occur. In contrast, during set, the drift and diffusion fluxes have the same direction which normally leads to sharp switching. The accurate device model further allows us to examine the different factors driving the switching process. The Vo drift and diffusion fluxes are determined by the diffusion coefficient (D) and drift velocity (v), respectively. These values are in turn functions of the characteristic hopping distance (a), with D and v (at high field) proportional to  $a^2$  and  $a \cdot \sinh(a)$ , respectively (Figure S2). Therefore, the drift flux is more sensitive to the hopping distance and becomes larger than the diffusion flux as a increases (Figure 4c), leading to more abrupt switching behaviors during the set and reset pulses. Figure 4d shows the calculated analog switching behavior at different values of a. Both the DC switching behaviors (Figure 4a) and pulse programming characteristics show distinctive differences between the device having the smallest a (0.1 nm) which shows clear gradual (e.g., analog) changes and the device having the largest a (0.2 nm) which shows essentially binary (e.g., digital) resistive switching. Additionally, because both the drift and diffusion fluxes increase with a, a switching material with larger a will yield a wider gap during the reset process and more lateral expansion during the set process (Figure 4b). As a result, a larger dynamic range (on/off ratio) can be obtained for devices having higher a values. It is clear from these

VOL.8 • NO.3 • 2369-2376 • 2014

IAI

www.acsnano.org

Figure 4. Hopping distance effects on analog switching. Calculated (a) DC I-V characteristics, (b) 2-D maps of  $n_D$  after the set process. (c) Diffusion and drift components D and v as a function of the hopping distance a under a high electric field (10<sup>7</sup> V/cm), and (d) analog switching behavior at different values of a.

discussions that, by tuning the material properties, particularly the characteristic hopping distance *a*, different switching dynamics can be obtained, with a large *a* resulting in larger resistance ratios and more abrupt switching, while a small *a* is preferred to obtain a more gradual transition.

Based on the simulation results, guidance to device design can be obtained by examining the relevant device parameters. For example, besides the effect of the hopping distance a, the thermal properties of the TE (*i.e.*, the thermal conductivity  $k_{th}$ ) also affect the analog switching behavior. As shown in Figure S6, as the  $k_{\rm th}$  of the TE increases, the heat generated by Joule heating can be easily dissipated through the TE, so the location of the depletion gap in the CF, that is, the location of the maximum temperature, is moved closer to the TE/Ta<sub>2</sub>O<sub>5</sub> interface (Figure S6b). In addition, the maximum temperature is also decreased by effective heat dissipation through the TE (Figure S6c). Consequently, both the drift and the diffusion fluxes are decreased, and a more gradual transition during the set process is observed. If however an abrupt set process is desirable for memory applications, a TE material with low  $k_{\rm th}$  will be preferred. The effects of the oxide thickness and the activation energy  $E_{a}$  are discussed in Supporting Information, as well.

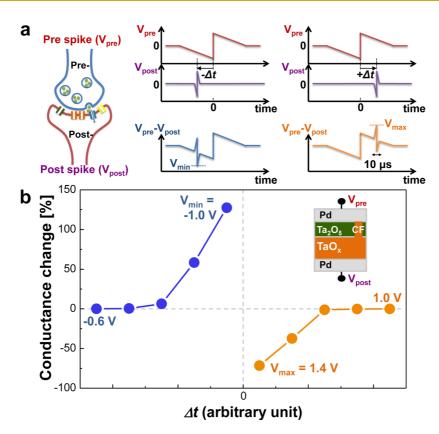

One potential application of the analog memristor devices is neuromorphic computing by emulating synaptic components. Synaptic connections dominate the architecture of biological networks and are crucial to perception and learning. An important synaptic learning rule is known as spike-timing-dependent plasticity (STDP),<sup>27</sup> which regulates the synaptic weights based on the relative spike timings of the presynaptic and postsynaptic neurons. The ability to emulate STDP learning in nanoelectronic synapse devices will enable memristor-based, brain-inspired neuromorphic computational systems.<sup>4,5,13</sup> Below we show possible pulsing schemes for implementing STDP for tantalumoxide-based memristors (Figure 5a). The prespike voltage ( $V_{pre}$ ) and postspike voltage ( $V_{post}$ ) are applied to the TE and the BE of the memristor, respectively. The net programming voltage ( $V_{pre} - V_{post}$ ) is applied across the device at the moments of positive or negative  $\Delta t$ .  $V_{\min}$  and  $V_{\max}$  are the minimum and maximum voltage amplitudes that can induce potentiation (set) and depression (reset) across the synapse (memristor), respectively. Figure 5b shows the simulated conductance change rate based on the accurate physical model as a function of the relative timing of the pre- and postspike voltage applications, with different  $V_{\min}$  or  $V_{\max}$ . It should be noted that this pulsing scheme is one of many possible ways to obtain STDP characteristics in memristors.<sup>4,5,28</sup> The simulated STDP characteristics are indeed consistent with the biological data measured in hippocampal glutamatergic synapses by Bi and Poo<sup>27</sup> or in other previous studies.<sup>4,5,13,28</sup> The accurate physical model proposed in this work thus will enable simulation of large-scale memristor-based neuromorphic systems and help

VOL. 8 • NO. 3 • 2369-2376 • 2014

IAI

www.acsnano.org

Figure 5. Achieving STDP with the tantalum oxide memristor. (a) One possible pulsing scheme to implement STDP for tantalum-oxide-based memristors. (b) Simulated conductance change as a function of the relative timing of pre- and postspikes.

continued improvement for designing appropriate materials or structures of synaptic devices.

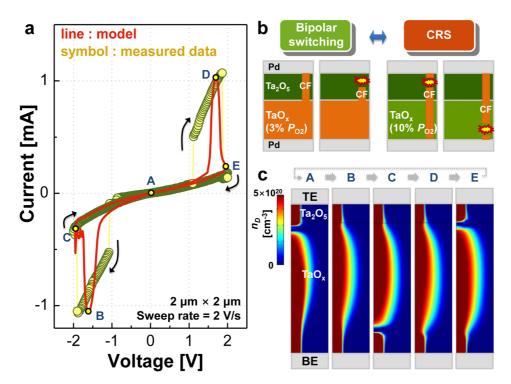

Finally, we show that our proposed model can be used to describe the rich dynamic effects observed in memristors. One such example is the recently observed complementary resistive switching (CRS) behavior which leads to a decrease in current at higher voltages due to depletion of  $V_{\rm O}$  at a different location in the oxide stack.<sup>29,30</sup> It is known that both the bipolar switching and the CRS behaviors can be obtained from tantalum oxide memristors, depending on the TaO<sub>x</sub> base layer stoichiometry.<sup>19,31</sup> When the TaO<sub>x</sub> base layer is very oxygen-poor, the device exhibits typical bipolar switching, as shown in Figure 1b. In this case, the  $TaO_x$ base layer contains a high concentration of  $V_{\Omega}$  and can act as an infinite reservoir of V<sub>O</sub>. Consequently, resistive switching (in other words, the formation/rupture of the CF) occurs only inside the Ta<sub>2</sub>O<sub>5</sub> layer. On the other hand, when the  $TaO_x$  base layer is only moderately oxygen-poor, the  $TaO_x$  base layer can no longer serve as an infinite V<sub>o</sub> reservoir and formation/rupture of the CF in the TaO<sub>x</sub> base layer is also possible, as depicted in Figure 6b. To simulate the CRS behavior, the initial  $V_{\rm O}$ concentration was assumed to be  $n_{\rm D} = 1 \times 10^{21} \, {\rm cm}^{-3}$ in both the  $Ta_2O_5$  and  $TaO_x$  layers, and the model successfully captures the CRS behavior (Figure 6a).

The nature of the CRS switching was revealed by the model by examining the distribution of  $n_D$  at the

different states of the device (e.g., A, B, C, D, and E depicted in Figure 6a) (Figure 6c). When the device is in state A, a  $V_{\rm O}$  depletion gap is formed inside the Ta<sub>2</sub>O<sub>5</sub> layer, so the overall conductance of the device is low. At negative voltages below -1 V,  $V_{O}$  migration leads to the completion of the conducting path and causes the overall conductance to increase, and the device reaches the intermediate, high conductance state B. However, at even higher negative voltages, a depletion gap is developed near the BE and the device is switched to another low conductance state C. Both states A and C show similar high resistances but represent different internal states, as represented by the locations of the depletion gap and shown in Figure 6c. A similar process also occurs at positive biases, involving states D and E. These studies, using only one set of parameters at different conditions, further reveal the rich switching dynamics in memristors and the importance of the complete physical model covering the dynamic evolution of the CF.

### CONCLUSION

By solving the local electric field, temperature, and  $V_{\rm O}$  concentration self-consistently, we developed a complete and accurate physical model that quantitatively explains the dynamic memristive switching process. Significantly, the model reveals that the conducting filament is ruptured and formed locally inside

VOL. 8 • NO. 3 • 2369-2376 • 2014

AGNANC www.acsnano.org

Figure 6. Complementary resistive switching behavior. (a) Measured and calculated CRS behavior when 10% the oxygen partial pressure ( $P_{O_2}$ ) during the reactive sputtering process was used during TaO<sub>x</sub> sputtering. The measured device size is 2  $\mu$ m × 2  $\mu$ m. In CRS simulation, activation energy for conduction ( $E_{AC}$ ) of Ta<sub>2</sub>O<sub>5</sub> is changed from 0.05 to 0.07 eV to provide a better fit with the experimental data. (b) Schematics explaining the evolution between bipolar switching and CRS for the different  $P_{O_2}$  values. (c) Calculated 2-D maps of  $n_D$  at different bias points (A, B, C, D, and E) depicted in (a).

the switching layer, and the set process involves field and thermal-driven filament formation followed by filament expansion, while the reset process is dominated by thermal-driven filament rupture followed by gap widening. The competition between the drift and diffusion components during reset can lead to different resistive switching characteristics. Differences in material properties (*i.e.*, hopping distance), device layout, and electrode selection can also affect the device performance, and the role of thermal effects can be significant. The proposed model allows accurate prediction of resistive switching characteristics for both DC and AC input signals and was able to reproduce the analog switching and CRS behaviors. We believe such in-depth analysis of the memristive switching process not only provides a reliable and accurate physical picture of the resistive switching process but also produces much-needed guidelines for continued design and optimization of this important class of devices for memory and logic applications.

#### **METHODS**

Device Fabrication. The memristor devices in this work with sizes ranging from 50 nm to 2  $\mu$ m were fabricated in a crossbar structure on SiO<sub>2</sub> (100 nm)/Si substrates with electrodes patterned using either e-beam lithography (Raith 150) or traditional photolithography (GCA AS200 AutoStep). First, the bottom Pd electrode was deposited by e-beam evaporation followed by lift-off processes. Next, the TaO<sub>x</sub> base layer was deposited by direct current (DC) reactive sputtering of a Ta metal target in an Ar/O2 gas mixture at 400 °C. The total pressure of Ar/O<sub>2</sub> was  $\sim$ 5 mTorr, and the oxygen partial pressure in the Ar/O<sub>2</sub> mixture was varied in the range of 3-10% in order to modulate the switching behavior of the devices. The Ta2O5 switching layer was then deposited by RF sputtering using a  $Ta_2O_5$  ceramic target at room temperature in Ar with a pressure of  ${\sim}5$  mTorr. The top Pd electrode was then deposited by e-beam evaporation followed by lift-off processes. Finally, a reactive ion etching process using SF<sub>6</sub>/Ar was performed to expose the bottom contacts. Figure S1 shows resistive switching behavior of the fabricated devices during forming, reset,

KIM ET AL.

and set steps. For the forming step, a resistor (5  $k\Omega$ ) is serially connected with the device to prevent permanent breakdown.

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. The authors would like to thank Dr. Y. Yang for help with TEM analysis, and J. Lee for useful discussions. This work was supported in part by the AFOSR through MURI Grant FA9550-12-1-0038 and by DARPA through cooperative agreement HR0011-13-2-0015. This work used the Lurie Nanofabrication Facility at the University of Michigan, a member of the National Nanotechnology Infrastructure Network (NNIN) funded by NSF. The views expressed are those of the author and do not reflect the official policy or position of the Department of Defense or the U.S. Government.

Supporting Information Available: Additional discussions about the detail model derivation steps and other parameters related to the resistive switching behavior. This material is available free of charge via the Internet at http:// pubs.acs.org.

#### **REFERENCES AND NOTES**

- Mead, C. Neuromorphic Electronic Systems. Proc. IEEE 1990, 78, 1629–1636.

- Fusi, S.; Annunziato, M.; Badoni, D.; Salamon, A.; Amit, D. Spike Driven Synaptic Plasticity: Theory, Simulation, VLSI Implementation. *Neural Comput.* 2000, *12*, 2227–2258.

- Likharev, K. K. Hybrid CMOS/Nanoelectronic Circuits: Opportunities and Challenges. J. Nanoelectron. Optoelectron. 2008, 3, 203–230.

- Jo, S. H.; Chang, T.; Ebong, I.; Bhadviya, B. B.; Mazumder, P.; Lu, W. Nanoscale Memristor Device as Synapse in Neuromorphic Systems. *Nano Lett.* **2010**, *10*, 1297–1301.

- Yu, S.; Wu, Y.; Jeyasingh, R.; Kuzum, D.; Wong, H.-S. P. An Electronic Synapse Device Based on Metal Oxide Resistive Switching Memory for Neuromorphic Computation. *IEEE Trans. Electron Devices* **2011**, *58*, 2729–2737.

- Laiho, M.; Lehtonen, E. Arithmetic Operation Within Memristor-Based Analog Memory. Proc. 12<sup>th</sup> International Workshop Cellular Nanoscale Networks and Their Applications (CNNA), Berkeley, CA, Feb. 3–5, 2010; pp 1–4.

- Chua, L. O. Memristor—The Missing Circuit Element. *IEEE Trans. Circuit Theory* 1971, CT-18, 507–519.

- Di Ventra, M.; Pershin, Y. V.; Chua, L. O. Circuit Elements with Memory: Memristors, Memcapacitors, and Meminductors. *Proc. IEEE* 2009, *97*, 1717–1724.

- Chua, L. Resistance Switching Memories Are Memristors. Appl. Phys. A: Mater. Sci. Process. 2011, 102, 765–783.

- Ambrogio, S.; Balatti, S.; Nardi, F.; Facchinetti, S.; Ielmini, D. Spike-Timing Dependent Plasticity in a Transistor-Selected Resistive Switching Memory. *Nanotechnology* 2013, 24, 384012–384012.

- 11. Chang, T.; Jo, S.-H.; Lu, W. Short-Term Memory to Long-Term Memory Transition in a Nanoscale Memristor. *ACS Nano* **2011**, *5*, 7669–7676.

- Alibart, F.; Zamanidoost, E.; Strukov, D. B. Pattern Classification by Memristive Crossbar Circuits Using *Ex Situ* and *In Situ* Training. *Nat. Commun.* **2013**, *4*, 2072.

- Zamarreno-Ramos, C.; Camunas-Mesa, L. A.; Perez-Carrasco, J. A.; Masquelier, T.; Serrano-Gotarredona, T.; Linares-Barranco, B. On Spike-Timing-Dependent-Plasticity, Memristive Devices, and Building a Self-Learning Visual Cortex. *Front. Neurosci.* 2011, *5*, 26.

- Strukov, D. B.; Williams, R. S. Exponential Ionic Drift: Fast Switching and Low Volatility of Thin-Film Memristors. *Appl. Phys. A: Mater. Sci. Process.* 2009, *94*, 515.

- Ielmini, D. The Universal Set/Reset Characteristics of Bipolar RRAM by Field- and Temperature-Driven Filament Growth. *IEEE Trans. Electron Devices* 2011, 58, 4309–4317.

- Chang, T.; Jo, S.-H.; Kim, K.-H.; Sheridan, P.; Gaba, S.; Lu, W. Synaptic Behaviors and Modeling of a Metal Oxide Memristive Device. *Appl. Phys. A: Mater. Sci. Process.* **2011**, *102*, 857–863.

- Eshraghian, K.; Kavehei, O.; Cho, K.-R.; Chappell, J. M.; Iqbal, A.; Al-Sarawi, S. F.; Abbott, D. Memristive Device Fundamental and Modeling: Application to Circuits and Systems Simulation. *Proc. IEEE* **2012**, *100*, 1991–2007.

- Yu, S.; Wong, H.-S. P. A Phenomenological Model for the Reset Mechanism of Metal Oxide RRAM. *IEEE Electron Device Lett.* 2010, *31*, 1455–1457.

- Nardi, F.; Balatti, S.; Larentis, S.; lelmini, D. Complementary Switching in Metal Oxides: Toward Diode-Less Crossbar RRAMs. 2011 IEEE International Electron Devices Meeting (IEDM), Washington, DC, Dec. 5–7, 2011; pp 31.1.1–31.1.4.

- Lee, M.-J.; Lee, C. B.; Lee, D.; Lee, S. R.; Chang, M.; Hur, J. H.; Kim, Y.-B.; Kim, C.-J.; Seo, D. H.; Seo, S.; *et al.* A Fast, High-Endurance and Scalable Non-volatile Memory Device Made from Asymmetric Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>2-x</sub> Bilayer Structures. *Nat. Mater.* **2011**, *10*, 625–630.

- Torrezan, A. C.; Strachan, J. P.; Medeiros-Ribeiro, G.; Williams, R. S. Sub-nanosecond Switching of a Tantalum Oxide Memristor. *Nanotechnology* **2011**, *22*, 485203.

- Yang, Y.; Choi, S.; Lu, W. Oxide Heterostructure Resistive Memory. Nano Lett. 2013, 13, 2908–2915.

- KIM ET AL.

- 23. Waser, R.; Dittmann, R.; Staikov, G.; Szot, K. Redox-Based Resistive Switching Memories-Nanoionic Mechanisms, Prospects, and Challenges. *Adv. Mater.* **2009**, *21*, 2632– 2663.

- Larentis, S.; Cagli, C.; Nardi, F.; lelmini, D. Filament Diffusion Model for Simulating Reset and Retention Processes in RRAM. *Microelectron. Eng.* 2011, 7, 1119–1123.

- Larentis, S.; Nardi, F.; Balatti, S.; Gilmer, D. C.; Ielmini, D. Resistive Switching by Voltage-Driven Ion Migration in Bipolar RRAM—Part II: Modeling. *IEEE Trans. Electron Devices* 2012, *59*, 2468–2475.

- Kim, S.; Kim, S.-J.; Kim, K. M.; Lee, S. R.; Chang, M.; Cho, E.; Kim, Y.-B.; Kim, C. J.; Chung, U.-I.; Yoo, I.-K. Physical Electrothermal Model of Resistive Switching in Bi-layered Resistance-Change Memory. *Sci. Rep.* **2013**, *3*, 1680.

- Bi, G. Q.; Poo, M. M. Synaptic Modifications in Cultured Hippocampal Neurons: Dependence on Spike Timing, Synaptic Strength, and Postsynaptic Cell Type. *J. Neurosci.* 1998, 2, 10464–10472.

- Seo, K.; Kim, I.; Jung, S.; Jo, M.; Park, S.; Park, J.; Shin, J.; Biju, K. P.; Kong, J.; Lee, K.; *et al.* Analog Memory and Spike-Timing-Dependent Plasticity Characteristics of a Nanoscale Titanium Oxide Bilayer Resistive Switching Device. *Nanotechnology* **2011**, *22*, 254023.

- Linn, E.; Rosezin, R.; Kugeler, C.; Waser, R. Complementary Resistive Switches for Passive Nanocrossbar Memories. *Nat. Mater.* 2010, 9, 403–406.

- Nardi, F.; Balatti, S.; Larentis, S.; Gilmer, D. C.; Ielmini, D. Complementary Switching in Oxide-Based Bipolar Resistive-Switching Random Memory. *IEEE Trans. Electron De*vices 2013, 60, 70–77.

- Yang, Y.; Sheridan, P.; Lu, W. Complementary Resistive Switching in Tantalum Oxide-Based Resistive Memory Devices. *Appl. Phys. Lett.* **2012**, *100*, 203112.